# Lecture 8: Intro to Assembly Programming

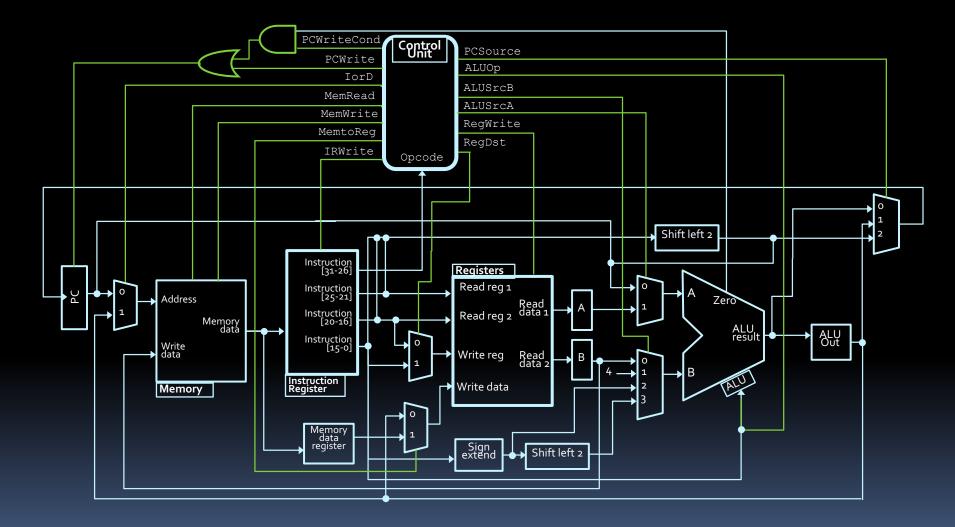

#### The MIPS Microprocessor

#### Intro to Machine Code

- Now that we have a processor, operations are performed by:

- The instruction register sends instruction components to the control unit.

- The control unit decodes instruction according to the opcode in the first 6 bits.

- The control unit sending a sequence of signals to the rest of the processor.

- Only questions remaining:

- Where do these instructions come from?

- How are they provided to the instruction memory?

#### Machine Code Instructions

| 00000200         6C         00         65         00         64         00         74         00         20         00         75         00           00000210         65         00         64         00         66         00         67         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00 | 00000010         0C         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         00         <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00 00<br>00 00<br>00 00<br>00 00<br>ea 00<br>ec 00<br>e2 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | $ \begin{array}{c} {\rm CC} & 80 \\ {\rm 53} & 00 \\ {\rm 00} & 00 \\ 00 & 00 \\ 00 & 00 \\ 00 & 00 \\ 00 & 00 \\ 00 & 00 \\ 00 & 00 \\ 00 & 00 \\ 00 & 00 \\ 00 & 00 \\ 00 & 00 \\ 00 & 00 \\ 00 & 00 \\ 00 & 00 \\ 00 \\ 00 & 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\ 00 \\$ |

| 7 5 6<br>1 e. c. t. R.u. l.<br>e. F.o.r. F.i.<br>1 e. x. y.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <pre>% S.<br/>e.l.e.c.t. R.u.<br/>l.e. M.S.<br/>.S.h.e.l.l. D.<br/>l.g.<br/>.PS. 6.2%.<br/>.P. V.A. J&amp;<br/></pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

#### A little about MIPS

#### MIPS

- Short for Microprocessor without Interlocked

Pipeline Stages

- A type of RISC (Reduced Instruction Set Computer) architecture.

- Provides a set of simple and fast instructions

- Compiler translates instructions into 32-bit instructions for instruction memory.

- Complex instructions are built out of simple ones by the compiler and assembler.

#### MIPS Memory and Instructions

All memory is addressed in bytes.

- Instruction addresses are measured in bytes, starting from the instruction at address o.

- All instructions are 32 bits (4 bytes) long

- Therefore:

all instruction addresses are divisible by 4.

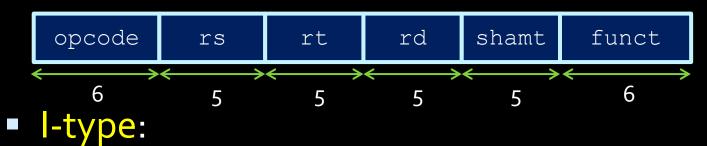

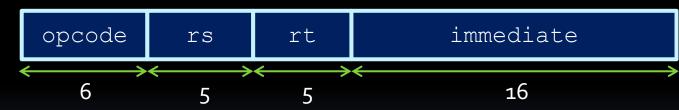

#### Recall: MIPS instruction types

#### R-type:

J-type:

#### MIPS Registers

- In MIPS is register-to-register (a.k.a. load-store) architecture

- Source, destination of ALU operations are registers.

- MIPS provides 32 registers.

- Some have special values:

- Register 0 (\$zero): value 0 always (writes to it are discarded)

- Register 1 (\$at): reserved for the assembler.

- Registers 28-31 (\$gp, \$sp, \$fp, \$ra): memory and function support

- Registers 26-27: reserved for OS kernel

- Some are used by programs as functions parameters:

- Registers 2-3 (\$vo, \$v1): return values

- Registers 4-7 (\$ao-\$a3): function arguments

- Some are used by programs to store values:

- Registers 8–15, 24–25 (\$to-\$tg): temporaries

- Registers 16-23 (\$so-\$s7): saved temporaries

- Also three special registers (PC, HI, LO) that are not directly accessible.

- HI and LO are used in multiplication and division, and have special instructions for accessing them.

#### Assembly Language Introduction

#### Assembly vs Machine Code

- Each processor type has its own language for representing 32-bit instructions as userreadable code words.

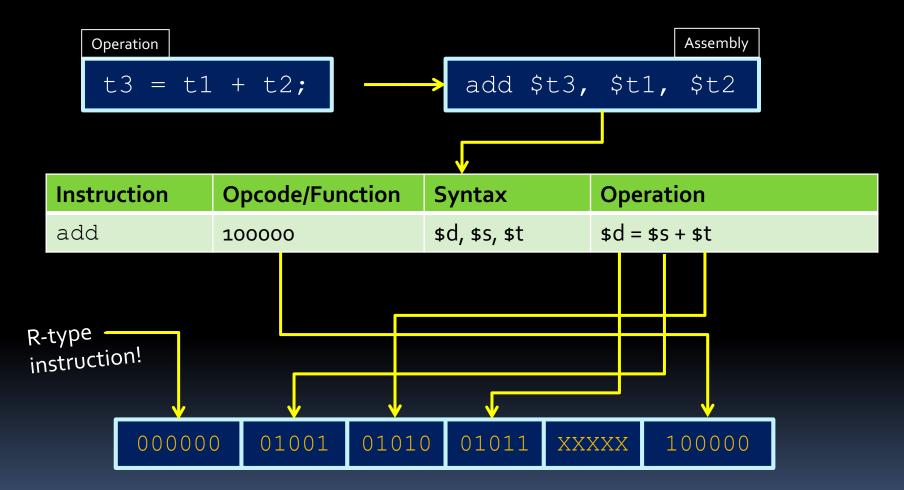

- **Example**: C = A + B

- Assume A is stored in \$t1, B in \$t2, C in \$t3.

- Assembly language instruction:

add \$t3, \$t1, \$t2 <

<u>Note:</u> There is a 1to-1 mapping for all assembly code and machine code instructions!

Machine code instruction:

000000 01001 01010 01011 XXXXX 100000

## Assembly language

- Assembly language is the lowest-level language that you'll ever program in.

- Many compilers translate their high-level program commands into assembly commands, which are then converted into machine code and used by the processor.

FORTRA

C

High-Level Language

Assembly Language

Pasca

<u>Note</u>: There are multiple types of assembly language, especially for different architectures!

#### Why learn assembly?

- Understand how code really works

- Better analyze code (runtime, control flows, pointers, stack overflows)

- Make you appreciate constructs of high level languages

- Connect your high level programming knowledge to hardware

- It's on the exam...

## Arithmetic instructions

| Instruction | Opcode/Function | Syntax        | Operation                      |

|-------------|-----------------|---------------|--------------------------------|

| add         | 100000          | \$d, \$s, \$t | \$d = \$s + \$t                |

| addu        | 100001          | \$d, \$s, \$t | \$d = \$s + \$t                |

| addi        | 001000          | \$t, \$s, i   | \$t = \$s + SE(i)              |

| addiu       | 001001          | \$t, \$s, i   | \$t = \$s + SE(i)              |

| div         | 011010          | \$s, \$t      | lo = \$s / \$t; hi = \$s % \$t |

| divu        | 011011          | \$s, \$t      | lo = \$s / \$t; hi = \$s % \$t |

| mult        | 011000          | \$s, \$t      | hi:lo = \$s * \$t              |

| multu       | 011001          | \$s, \$t      | hi:lo = \$s * \$t              |

| sub         | 100010          | \$d, \$s, \$t | \$d = \$s - \$t                |

| subu        | 100011          | \$d, \$s, \$t | \$d = \$s - \$t                |

Note: "hi" and "lo" refer to the high and low bits referred to in the register slide. "SE" = "sign extend".

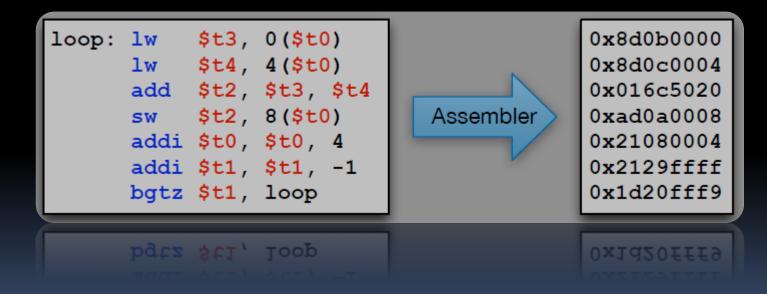

#### Assembly $\rightarrow$ Machine Code

Although we specify "don't care" bits as X values, the assembler generally assigns some value (like o).

## Logical instructions

| Instruction | Opcode/Function | Syntax        | Operation          |

|-------------|-----------------|---------------|--------------------|

| and         | 100100          | \$d, \$s, \$t | \$d = \$s & \$t    |

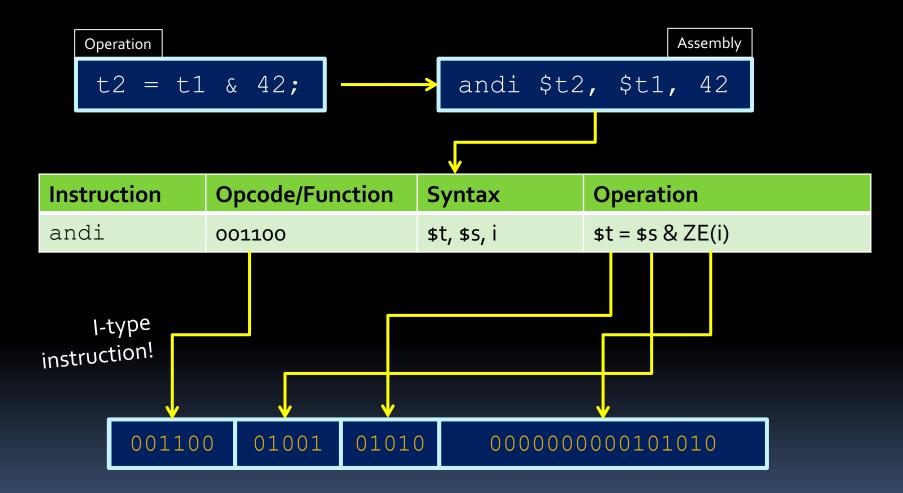

| andi        | 001100          | \$t, \$s, i   | \$t = \$s & ZE(i)  |

| nor         | 100111          | \$d, \$s, \$t | \$d = ~(\$s   \$t) |

| or          | 100101          | \$d, \$s, \$t | \$d = \$s   \$t    |

| ori         | 001101          | \$t, \$s, i   | \$t = \$s   ZE(i)  |

| xor         | 100110          | \$d, \$s, \$t | \$d = \$s ^ \$t    |

| xori        | 001110          | \$t, \$s, i   | \$t = \$s ^ ZE(i)  |

Note: ZE = zero extend (pad upper bits with 0 value).

#### Assembly $\rightarrow$ Machine Code II

#### Shift instructions

| Instruction | Opcode/Function | Syntax        | Operation         |

|-------------|-----------------|---------------|-------------------|

| sll         | 000000          | \$d, \$t, a   | \$d = \$t << a    |

| sllv        | 000100          | \$d, \$t, \$s | \$d = \$t << \$s  |

| sra         | 000011          | \$d, \$t, a   | \$d = \$t >> a    |

| srav        | 000111          | \$d, \$t, \$s | \$d = \$t >> \$s  |

| srl         | 000010          | \$d, \$t, a   | \$d = \$t >>> a   |

| srlv        | 000110          | \$d, \$t, \$s | \$d = \$t >>> \$s |

Note: srl = "shift right logical" sra = "shift right arithmetic". The "v" denotes a variable number of bits, specified by \$s. a is shift amount, and is stored in shamt when encoding the R-type machine code instructions.

#### Data movement instructions

| Instruction | Opcode/Function | Syntax | Operation |

|-------------|-----------------|--------|-----------|

| mfhi        | 010000          | \$d    | \$d = hi  |

| mflo        | 010010          | \$d    | \$d = lo  |

| mthi        | 010001          | \$S    | hi = \$s  |

| mtlo        | 010011          | \$S    | lo = \$s  |

These are instructions for operating on the HI and LO registers described earlier (for multiplication and division)

#### ALU instructions in RISC

- Most ALU instructions are R-type instructions.

- The six-digit codes in the tables are therefore the function codes (opcodes are 000000).

- Exceptions are the I-type instructions (addi, andi, ori, etc.)

- Not all R-type instructions have an I-type equivalent.

- RISC principle dictate that an operation doesn't need an instruction if it can be performed through multiple existing operations.

- Example: addi + div → divi

#### Pseudoinstructions

Move data from \$t4 to \$t5?

move \$t5,\$t4 →

add \$t5,\$t4,\$zero

Multiply and store in \$\$1?

mul \$\$1,\$t4,\$t5 →

mult \$t4,\$t5 mflo \$s1

#### Time for a Break

Bill Watterson: Calvin & Hobbes

#### Making an assembly program

- Assembly language programs typically have structure similar to simple Python or C programs:

- They set aside registers to store data.

- They have sections of instructions that manipulate this data.

- It is always good to decide at the beginning which registers will be used for what purpose!

- More on this later <sup>(3)</sup>

# Time to write our first assembly program

#### Compute result = $a^2 + 2b + 10$

- Set up values in registers

a → \$to, b → \$t1

temp → \$t6

- temp = 10

- temp = temp + b

- temp = temp + b (again!)

- result = a\*a

- result = result + temp

|                      | \$t0,<br>\$t1,   |       |      | 7<br>9 |

|----------------------|------------------|-------|------|--------|

| addi                 | \$t6,            | \$zer | , ۲۰ | 10     |

|                      | 5t6, 9<br>5t6, 9 |       |      |        |

| mult<br>mflo<br>mfhi |                  | \$t0  |      |        |

| add s                | \$t4, \$         | \$t4, | \$te | 5      |

#### Formatting Assembly Code

- Instruction are written

- **as:** <instr> <parameters>

- Each instruction is written on its own line

- 3 columns

- Labels

- Code

- Comments

- Start with .text (we'll see other options later)

- First line of code to run = label: main

```

# Compute the following result: r = a^2 + 2b + 10

.text

# load up some values to test

main: addi $t0, $zero, 7

addi $t1, $zero, 9

# $t0 will be a, $t1 will be b, $t5:$t4 will be r

# $t6 will be temp

addi $t6, $zero, 10 # add 10 to r

add $t6, $t6, $t1 # then add b

add $t6, $t6, $t1 # then add b again

mult $t0, $t0  # multiply a * a

mflo $t4

# move the low result of a^2

# into the low register of r

# move the high result of a^2

mfhi $t5

# into the high register of r

add $t4, $t4, $t6

# add the temporary value

# (2b + 10) to the low

# register of r

```

#### Simulating MIPS

#### aka: QtSpim

| FP Regs                  | Int Regs [16] | Data        | Text         |            |          |          |                                 |  |

|--------------------------|---------------|-------------|--------------|------------|----------|----------|---------------------------------|--|

| int Regs [16]            | 8×            | 1000 C      |              |            |          |          |                                 |  |

|                          | 400048        |             | egment [1000 |            | 40000]   |          |                                 |  |

|                          | 0             |             | [1000ffff]   |            |          |          |                                 |  |

|                          | 0             | [10010000]  |              | 00033667   | 00033767 | 00000000 | E # g 6 g 7                     |  |

| BadVAddr =               |               | [10010010]. | [1003ffff]   | 00000000   | т        |          |                                 |  |

| Status =                 | 3000ff10      |             |              |            | T        |          |                                 |  |

| HI =                     | 0             | User Stack  | [7ffff690]   | [80000000] |          |          |                                 |  |

| L0 =                     | 0             | {7ffff690]  | 00000003     | 7ffff79b   | 7ffff790 | 7ffff779 |                                 |  |

|                          |               | [7fffff6a0] | 00000000     | 7fffffd6   | 7fffffb7 | 7fffff91 |                                 |  |

| R0 [r0] =                | 0             | [7ffff6b0]  | 7fffff5a     | 7fffffle   | 7ffffeed | 7ffffeb5 | z                               |  |

| R1 [at] =                | 10010000      | [7ffff6c0]  | 7ffffe9c     | 7ffffe78   | 7ffffe51 | 7ffffe3d | x Q =                           |  |

| R2 [v0] =                |               | [7ffff6d0]  |              | 7ffffelb   |          |          | 0                               |  |

| R3 [v1] =                |               | [7ffff6e0]  | 7ffffdbe     | 7ffffdaf   | 7ffffd63 | 7ffffd02 |                                 |  |

| R4 [a0] =                | 3             | [7fffffff]  | 7ffffceb     | 7ffffodd   | 7ffffb95 | 7ffffb57 |                                 |  |

|                          | 7ffff694      | [7ffff700]  |              | 7ffffblf   |          | 7ffffac5 | <                               |  |

|                          | 7ffff6a4      | [7ffff710]  | 7ffffaad     | 7ffffa92   |          |          | n E                             |  |

| R7 [a3] =                |               | (7ffff720)  | 7ffffa27     | 7ffff9e6   |          |          |                                 |  |

| R8 [t0] =                |               | 17ffff7301  | 75555988     | 75555974   |          |          | t a B                           |  |

| R9 [t1] =                |               | [7ffff740]  |              | 7ffff916   |          |          | <                               |  |

| R10 [t2] =               |               | [7ffff750]  |              | 7ffff867   |          |          | g P B                           |  |

| R11 [t3] =               |               | [7ffff760]  |              | 7ffff816   |          |          | (                               |  |

| R12 [t4] =               |               | [7ffff770]  |              | 00000000   |          |          |                                 |  |

| R13 [t5] =               |               | [7ffff780]  |              | 6d617865   |          |          | moryexample.asm.                |  |

| R14 [t6] =               |               | [7ffff790]  |              | 45216c61   |          |          | School/ECE.C:/Us                |  |

| R15 [t7] =               |               | [7ffff7a0]  |              | 6e686f4a   |          |          | ers/John/Documen                |  |

| R16 (s0) =               |               | [7ffff7b0]  |              | 006e686f   |          |          | ts/John.windows                 |  |

| R17 [s1] =               |               | [7ffff7c0]  |              | 5£676e69   |          |          | tracing logfile =               |  |

| R18 [s2] =               |               | [7ffff7d0]  | 425c3a43     | 69425456   |          |          | C:\BVTBin\Tests\                |  |

| R19 [83] =               |               | [7ffff7e0]  |              | 706c6c61   |          |          | installpackage\c                |  |

| R20 [s4] =               |               | [7ffff7f0]  | 6f6c6973     |            | 616c2e65 |          | silogfile.log.wi                |  |

| R21 [\$5] =              |               | [7ffff8001  |              | 72745173   |          |          | ndows tracing fl                |  |

| R21 [85] =               |               | [7ffff810]  |              | 69770033   |          |          | ags=3.windir=C:\                |  |

| R23 [s7] =               |               | [7ffff820]  |              | 0073776f   |          |          | Windows, USERPROF               |  |

| R23 [87] =<br>R24 [t8] = |               | [7ffff830]  |              | 555c3a43   |          |          | ILE=C:\Users\Joh                |  |

| R24 [t8] = R25 [t9] =    |               | [7ffff840]  |              | 414e5245   |          | 006e686f |                                 |  |

|                          |               | [7ffff850]  |              | 414d4f44   |          |          | n. USERNAME = John.             |  |

| R26 [k0] =               |               |             |              |            |          |          | USERDOMAIN = John -             |  |

| R27 [k1] =               | 0 💌           | [7ffff860]  | 7470616C     | 5400706f   | 41435456 | 4e414d4d | l a p t o p . T V T C O M M O N |  |

SPIM is distributed under a BSD license

See the file README for a full copyright notice

The second secon

El Cittingi Interes sentes series actives Tables Darba

## QtSpim Simulator

- Link to download:

- <u>http://spimsimulator.sourceforge.net</u>

- MIPS settings in the simulator:

- From menu, Simulator  $\rightarrow$  Settings

- Important to not have "delayed branches" or "delayed loads" selected under Settings.

- "Load exception handler" field should also be unchecked.

- You should view user code (Text Segment -> User text), no need for "kernel text"

### QtSpim Settings

| ytSpim Sett   | ings                                    |                      |                                                 | ? | × |

|---------------|-----------------------------------------|----------------------|-------------------------------------------------|---|---|

| MIPS          | QtSpim                                  |                      |                                                 |   |   |

| MIPS Simulat  | tion Settings                           |                      |                                                 |   |   |

|               | achine<br>Delayed Branches<br>Mapped IO |                      | Accept Pseudo Instructions Enable Delayed Loads |   |   |

|               | Simple Machine                          |                      | Bare Machine                                    |   |   |

| Exception Har | ception Handler                         | File<br>e default ex | < <spim exception="" handler="">&gt;</spim>     |   |   |

## QtSpim – Quick How To

- Write a MIPS program (similar to the ones posted) in any text editor. Save it with .asm extension.

- In QtSpim select:

- File -> Reinitialize and load a file

- Single step through your program while observing (a) the Int Regs window and (b) the text window (user text).

- As you step through, the highlighted instruction is the one about to be executed.

#### QtSpim Help => MIPS reference

- OtSpim help (Help -> View Help) contains

- "Appendix A (Assemblers, Linkers, and the SPIM Simulator)" from Patterson and Hennessey, Computer Organization and Design: The Hardware/Software Interface, Third Edition

- Useful reference for MIPS R2000 Assembly Language

- Look at "Arithmetic and Logical Instructions".

r = (2a + 5) \* (7b)

```

.text

# $t0 = a, $t1 = b, $t4 = r

# $t7 = left side, $t8 = right side

main: addi $t0, $zero, 7 # load up some values to test

addi $t1, $zero, 9

# calculate left side

calc_left: add $t7, $t0, $t0 # ls <- 2a

addi $t7, $t7, 5 # ls <- ls + 5

# calculate right side

calc_right: addi $t8, $zero, 7 # rs <- 7</pre>

mult $t8, $t1  # multiply b * 7

mflo $t8  # put result back into rs

# multiply left * right and put result into r

mulitply: mult $t7, $t8

mflo $t4

```

#### Control Flow

### Control flow in assembly

Not all programs follow a linear set of instructions.

- Some operations require the code to branch to one section of code or another (if/else).

- Some require the code to jump back and repeat a section of code again (for/while).

- For this, we have labels on the left-hand side that indicate the points that the program flow might need to jump to.

- References to these points in the assembly code are resolved by the assembler at compile time to offset values for the program counter.

# Time for more instructions!

#### Branch instructions

| Instruction | Opcode/Function | Syntax          | Operation                  |

|-------------|-----------------|-----------------|----------------------------|

| beq         | 000100          | \$s, \$t, label | if (\$s == \$t) pc ← label |

| bgtz        | 000111          | \$s, label      | if (\$s > o) pc ← label    |

| blez        | 000110          | \$s, label      | if (\$s <= o) pc ← label   |

| bne         | 000101          | \$s, \$t, label | if (\$s != \$t) pc ← label |

- Branch operations are key when implementing if statements and while loops.

- The labels are memory locations, assigned to each label at compile time.

### Branch instructions

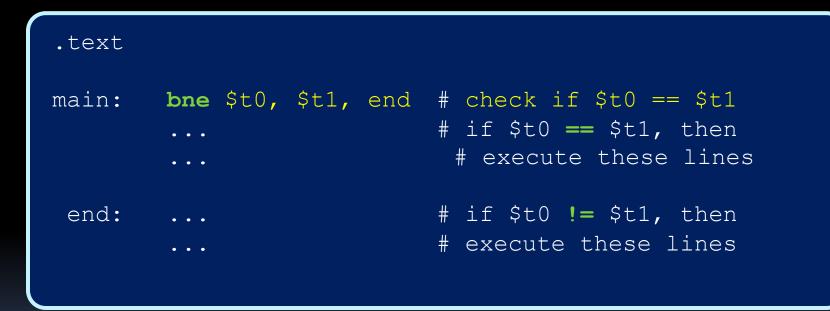

How does a branch instruction work?

## Branch instructions

Alternate implementation using bne:

Used to produce if statement behaviour.

## Conditional Branch Terms

- When the branch condition is met, we say the branch is taken.

- When the branch condition is not met, we say the branch is not taken.

- What is the next PC in this case?

- It's the usual PC+4

- How far can a processor branch? Are there any constraints?

# Jump instructions

| Instruction | Opcode/Function | Syntax      | Operation             |

|-------------|-----------------|-------------|-----------------------|

| j           | 000010          | label       | pc <del>(</del> label |

| jal         | 000011          | label       | \$ra = pc; pc ← label |

| jalr        | 001001          | <b>\$</b> S | \$ra = pc; pc = \$s   |

| jr          | 001000          | \$S         | pc = \$s              |

#### jal = "jump and link".

- Register \$31 (aka \$ra) stores the address that's used when returning from a subroutine.

- Note: jr and jalr are not j-type instructions.

# Comparison instructions

| Instruction | Opcode/Function | Syntax        | Operation           |

|-------------|-----------------|---------------|---------------------|

| slt         | 101010          | \$d, \$s, \$t | \$d = (\$s < \$t)   |

| sltu        | 101001          | \$d, \$s, \$t | \$d = (\$s < \$t)   |

| slti        | 001010          | \$t, \$s, i   | \$t = (\$s < SE(i)) |

| sltiu       | 001001          | \$t, \$s, i   | \$t = (\$s < SE(i)) |

#### "slt" = "Set Less Than"

- Comparison operation stores a one in the destination register if the less-than comparison is true, and stores a zero in that location otherwise.

- Signed: 0x8000000 is less than all numbers

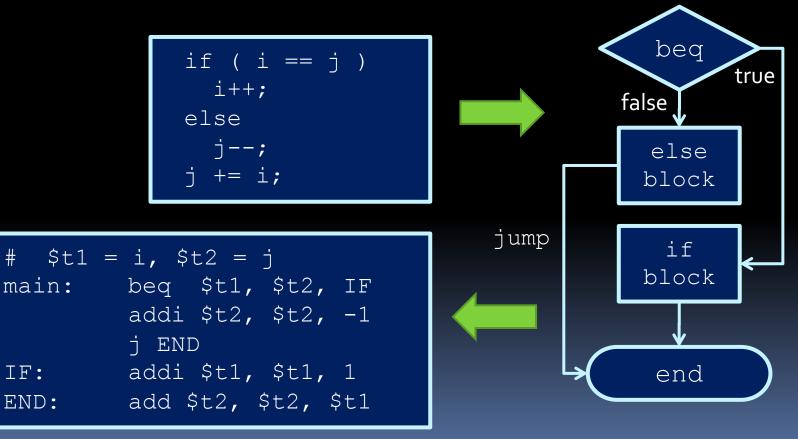

## If/Else statements in MIPS

- Strategy for if/else statements:

- Test condition, and jump to if logic block whenever condition is true.

- Otherwise, perform else logic block, and jump to first line after if logic block.

## Translated if/else statements

| # \$t1 = | = i, \$t2 = j        |                        |

|----------|----------------------|------------------------|

| main:    | beq \$t1, \$t2, IF   | # branch if ( i == j ) |

|          | addi \$t2, \$t2, -1  | # j                    |

|          | j END                | # jump over IF         |

| IF:      | addi \$t1, \$t1, 1   | # i++                  |

| END:     | add \$t2, \$t2, \$t1 | # j += i               |

Alternately, you can branch on the else condition first:

| # \$t1 = i, \$t2 = j |                      |                          |  |

|----------------------|----------------------|--------------------------|--|

| main:                | bne \$t1, \$t2, ELSE | # branch if ! ( i == j ) |  |

|                      | addi \$t1, \$t1, 1   | # i++                    |  |

|                      | j END                | # jump over ELSE         |  |

| ELSE:                | addi \$t2, \$t2, -1  | # j                      |  |

| END:                 | add \$t2, \$t2, \$t1 | # j += i                 |  |

# A trick with if statements

Use flow charts to help you sort out the control flow of the code:

### Multiple Conditions Inside If

## Multiple Conditions Inside If

#### Branch statement for each condition:

| # \$t1 = i, \$t2 = j, \$t3 = k |                      |                                 |  |

|--------------------------------|----------------------|---------------------------------|--|

| main:                          | beq \$t1, \$t2, IF   | # cond1: branch if ( i == j )   |  |

|                                | bne \$t1, \$t3, ELSE | # cond2: branch if ( i $!= k$ ) |  |

| IF:                            | addi \$t1, \$t1, 1   | # if (i==j i==k) → i++          |  |

|                                | j END                | # jump over else                |  |

| ELSE:                          | addi \$t2, \$t2, -1  | # else-body: j                  |  |

| END:                           | add \$t2, \$t1, \$t3 | # j = i + k                     |  |

# Multiple if conditions

How would this look if the condition changed?

| # \$t1 = i, \$t2 = j, \$t3 = k |                      |                                          |  |

|--------------------------------|----------------------|------------------------------------------|--|

| main:                          | bne \$t1, \$t2, ELSE | <pre># cond1: branch if ( i != j )</pre> |  |

|                                | bne \$t1, \$t3, ELSE | # cond2: branch if ( i $!= k$ )          |  |

| IF:                            | addi \$t1, \$t1, 1   | # if (i==j i==k) → i++                   |  |

|                                | j END                | # jump over else                         |  |

| ELSE:                          | addi \$t2, \$t2, -1  | # else-body: j                           |  |

| END:                           | add \$t2, \$t1, \$t3 | # j = i + k                              |  |

| main:  | add \$t0, \$zero, \$zero<br>addi \$t1, \$zero, 100 |

|--------|----------------------------------------------------|

| START: | beq \$t0, \$t1, END                                |

|        | addi \$t0, \$t0, 1                                 |

|        | j START                                            |

| END:   |                                                    |

# Loops in MIPS

Example of a simple loop, in assembly:

| main:  | add \$t0, \$zero, \$zero<br>addi \$t1, \$zero, 100   |

|--------|------------------------------------------------------|

| START: | beq \$t0, \$t1, END<br>addi \$t0, \$t0, 1<br>j START |

| END:   |                                                      |

...which is the same as saying (in C):

## Loops in MIPS

For loops (such as above) are usually implemented with the following structure:

| main:   | <init></init>                      |

|---------|------------------------------------|

| START:  | if (! <cond>) branch to END</cond> |

|         | <for-body></for-body>              |

| UPDATE: | <update></update>                  |

|         | jump to START                      |

| END:    |                                    |

### Loop example in MIPS

j = 0; for ( i=0 ; i<100 ; i++ ) { j = j + i; }

#### This translates to:

| # \$t0 = i, \$t1 = j           |                               |

|--------------------------------|-------------------------------|

| main: add \$t0, \$zero, \$zero | # set i to O                  |

| add \$t1, \$zero, \$zero       | # set j to O                  |

| addi \$t9, \$zero, 100         | # set \$t9 to 100             |

| START: beq \$t0, \$t9, EXIT    | <pre># branch if i==100</pre> |

| add \$t1, \$t1, \$t0           | # j = j + i                   |

| UPDATE: addi \$t0, \$t0, 1     | # i++                         |

| j START                        |                               |

| EXIT:                          |                               |

while loops are the same, without the initialization and update sections.

### Homework

- Fibonacci sequence:

- How would you convert this into assembly?

```

int n = 10;

int f1 = 1, f2 = 1;

while (n != 0) {

f1 = f1 + f2;

f2 = f1 - f2;

n = n - 1;

}

# result is f1

```