| CSC B58 Winter 2018 Midterm Test Duration — 1 hour and 50 minutes Aids allowed: none  Last Name:                                                                                                                                                                                                                                              | TITTO D. I                                                                                                |                                                         |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------|--|--|--|

| Question 0. [1 MARK]  Read and follow all instructions on this page, and fill in all fields appropriately.                                                                                                                                                                                                                                    |                                                                                                           |                                                         |  |  |  |

| (Please fill out the identification                                                                                                                                                                                                                                                                                                           | ntil you have received the signal section above, write your nand read the instructions below.  Good Luck! | ame on the back                                         |  |  |  |

| <ul> <li>This exam is double-sided, and consists of this one). When you receive the signal to have all pages.</li> <li>If you use any space for rough work marked.</li> <li>Do not remove any pages from the example of the example.</li> <li>Read all instructions before complete.</li> <li>Write your name and student numbers.</li> </ul> | b start, please make sure that you k, indicate clearly what you want exam booklet.  ting any questions    | # 0:/ 1 # 1:/ 4 # 2:/ 4 # 3:/10 # 4:/ 6 # 5:/ 5 # 6:/10 |  |  |  |

|                                                                                                                                                                                                                                                                                                                                               |                                                                                                           | TOTAL: /40                                              |  |  |  |

# Question 1. [4 MARKS]

Draw a circuit (built from transistors) for a XNOR gate.

#### Question 2. [4 MARKS]

Consider the Verilog code below:

```

module mystery(A, B, Clk, C, D);

input A, B, Clk;

output reg C, D;

always @ (A, B, Clk)

if (Clk & (A | B))

begin

if (A & ~B)

D = 1;

else

D = 0;

if (B & ~A)

C = 1;

else

C = 0;

end

endmodule

```

Briefly explain what this module does:

#### Question 3. [10 MARKS]

Consider the circuit description given below:

If A is high, we want X to have the same value as B, if A is off and C and D are both high, X should be on. Y acts as A XOR B whenever C is high.

Part (a) [2 MARKS]

Draw the truth table

#### Part (b) [8 MARKS]

Use K-map reduction to produce a SOM expression of X and a POM expression for Y. Show your work.

## Question 4. [6 MARKS]

Calculate -13d \* -7d using booth's algorithm. Show your work.

### Question 5. [5 MARKS]

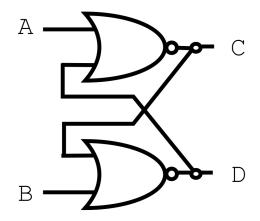

Complete the temporal truth table (time going down) for the given circuit

| time | A | В | С | D |

|------|---|---|---|---|

| 0    | 0 | 0 |   |   |

| 1    | 0 | 1 |   |   |

| 2    | 0 | 0 |   |   |

| 3    | 1 | 0 |   |   |

| 4    | 0 | 1 |   |   |

#### Question 6. [10 MARKS]

Consider the system described below:

The alarm system can be toggled between armed and disarmed mode by flipping the 'arm/disarm' switch. In armed mode, if the alarm is tripped, it will go into active mode causing a siren to sound. The alarm shouldn't do anything in disarmed mode. When the system is in active mode, it will stay that way until the 'arm/disarm' button is pressed, which will put it back into disarmed mode. Also, there is a debug switch which will put it into maintenance mode no matter what it's currently doing. Once the debug switch is turned off, the system goes into disarmed mode.

Draw the FSM diagram for this system, and give the flip-flop assignment for each state.

| Last Name: | First Name: |  |

|------------|-------------|--|